CDCU877 1.8-V PHASE CLOCK LOOP CLOCK DRIVER 说明书

发布者:wx****1f

2025-09-20

257 KB

15 页

文件列表:

CDCU877 1.8-V PHASE CLOCK LOOP CLOCK DRIVER 说明书.pdf |

下载文档 |

资源简介

>

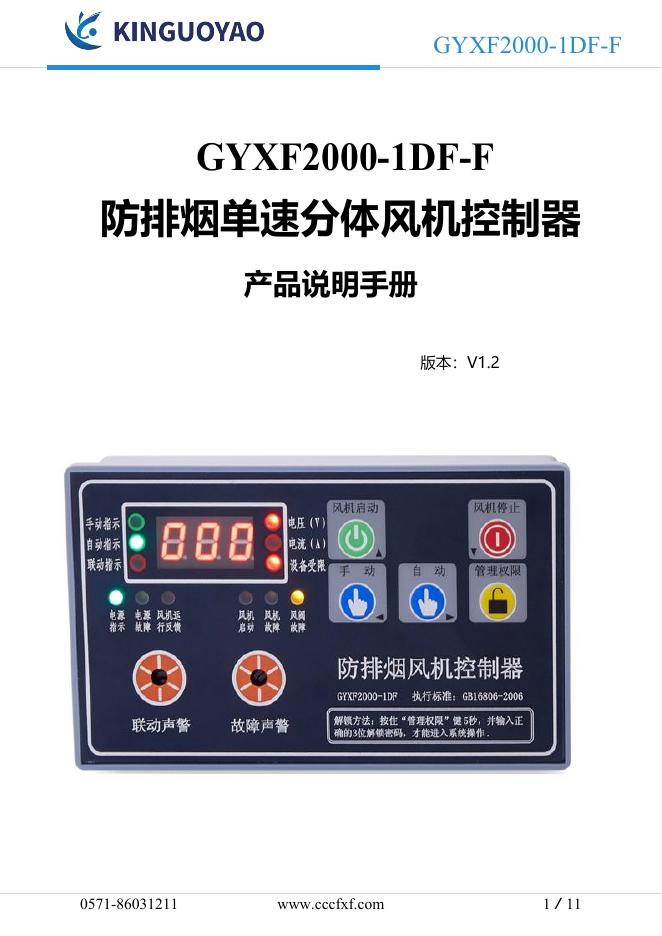

CDCU877是一种高性能、低抖动、低偏差、零延迟的缓冲器,用于将差分时钟输入对(CK,CK)分配给十对差分时钟输出(Yn,Yn)和一对差分时钟反馈输出(FBOUT,FBOUT)。时钟输出受到输入时钟(CK,CK),反馈时钟(FBIN,FBIN),LVCMOS控制引脚(OE,OS)和模拟功率输入(AVDD)的控制。当OE为低电平时,时钟输出(除了FBOUT/FBOUT)被禁用,而内部PLL继续保持锁定的频率。OS(输出选择)是一个必须连接到GND或VDD的可编程引脚。当OS为高电平时,OE的功能如上所述。当OS和OE都为低电平时,OE对Y7/Y7没有影响,它们是自由运行的。

加载中...

已阅读到文档的结尾了